# 6.976 High Speed Communication Circuits and Systems Lecture 5 High Speed, Broadband Amplifiers

Michael Perrott

Massachusetts Institute of Technology

Copyright © 2003 by Michael H. Perrott

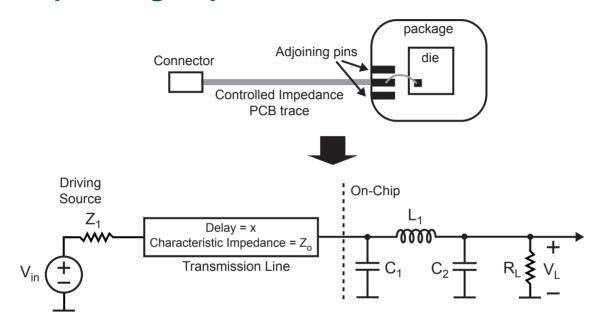

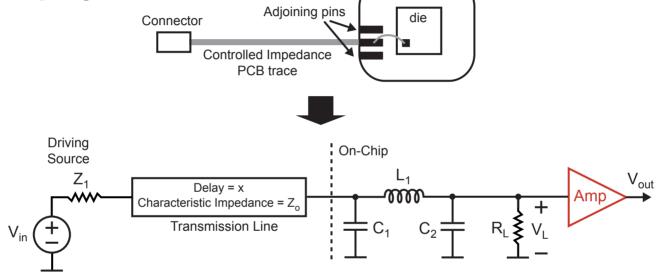

#### **Broadband Communication System**

Example: high speed data link on a PC board

- We've now studied how to analyze the transmission line effects and package parasitics

- What's next?

#### High Speed, Broadband Amplifiers

The first thing that you typically do to the input signal

package

is amplify it

- Function

- Boosts signal levels to acceptable values

- Provides reverse isolation

- Key performance parameters

- Gain, bandwidth, noise, linearity

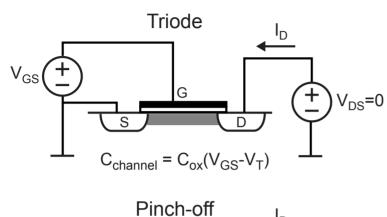

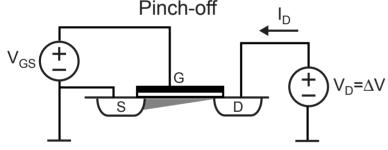

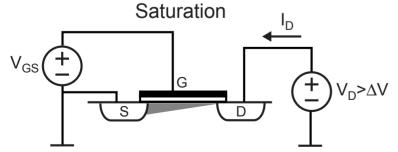

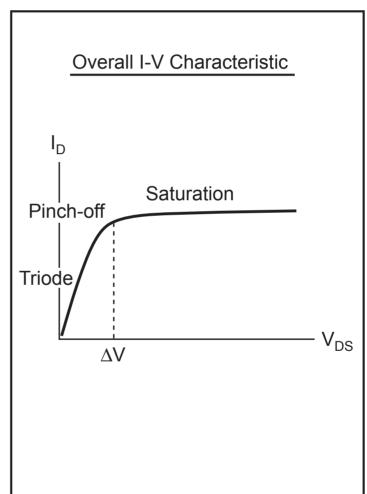

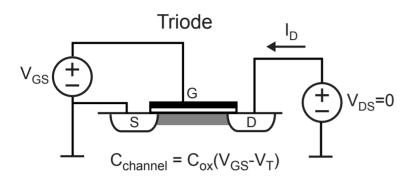

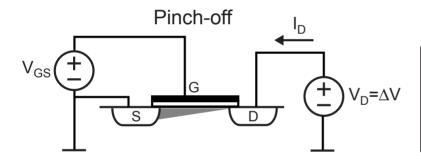

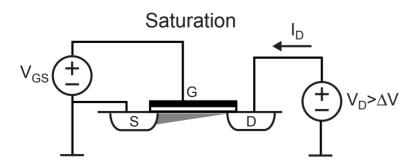

## Basics of MOS Large Signal Behavior (Qualitative)

#### Basics of MOS Large Signal Behavior (Quantitative)

$$I_{D} = \mu_{n}C_{ox}\frac{W}{L}(V_{GS} - V_{T} - V_{DS}/2)V_{DS}$$

$$\frac{\text{for }V_{DS} << V_{GS} - V_{T}}{I_{D} \approx \mu_{n}C_{ox}\frac{W}{L}(V_{GS} - V_{T})V_{DS}}$$

$$\Delta V = V_{GS} - V_{T}$$

$$\Delta V = \sqrt{\frac{2I_{D}L}{\mu_{n}C_{ox}W}}$$

$$\begin{array}{|c|c|} \hline + \\ V_D > \Delta V \end{array} & I_D = \frac{1}{2} \, \mu_n C_{ox} \frac{W}{L} \, (V_{GS} - V_T)^2 (1 + \lambda V_{DS}) \\ & \text{(where $\lambda$ corresponds to channel length modulation)} \end{array}$$

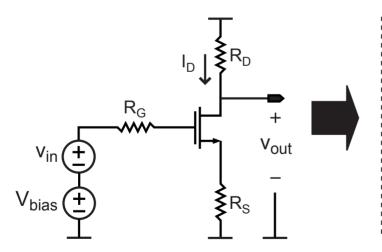

#### Analysis of Amplifier Behavior

- Typically focus on small signal behavior

- Work with a linearized model such as hybrid-π

- Thevenin modeling techniques allow fast and efficient analysis

- To do small signal analysis:

#### Small Signal Analysis Steps

- 1) Solve for bias current I<sub>d</sub>

- 2) Calculate small signal parameters (such as g<sub>m,</sub> r<sub>o</sub>)

- 3) Solve for small signal response using transistor hybrid- $\pi$  small signal model

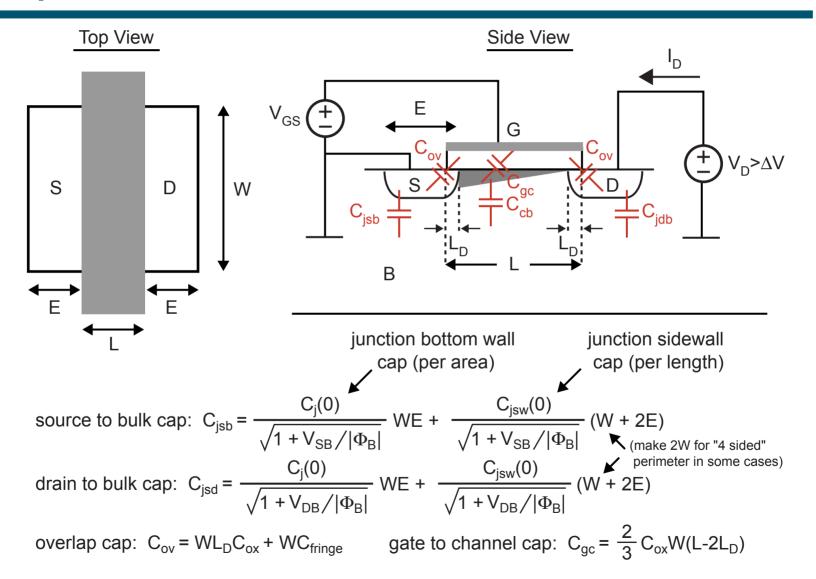

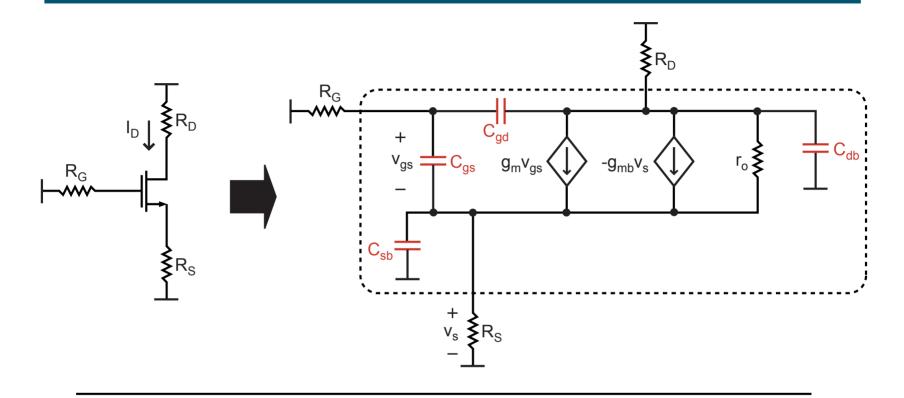

#### MOS DC Small Signal Model

Assume transistor in saturation:

Thevenin modeling based on the above

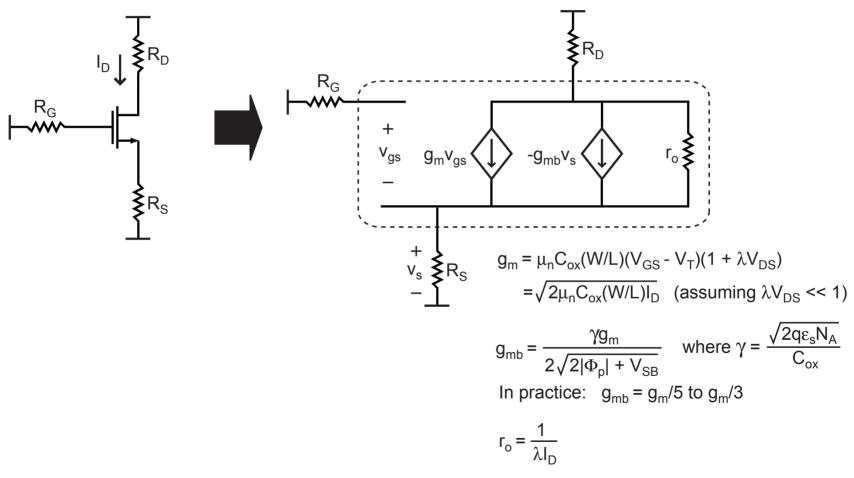

#### Capacitors For MOS Device In Saturation

channel to bulk cap: C<sub>cb</sub> - ignore in this class

#### MOS AC Small Signal Model (Device in Saturation)

$$\begin{split} &C_{gs} = C_{gc} + C_{ov} = \frac{2}{3} \, C_{ox} W (\text{L-2L}_{\text{D}}) + C_{ov} \\ &C_{gd} = C_{ov} \\ &C_{sb} = C_{jsb} \quad \text{(area + perimeter junction capacitance)} \\ &C_{db} = C_{jdb} \quad \text{(area + perimeter junction capacitance)} \end{split}$$

#### Wiring Parasitics

- Capacitance

- Gate: cap from poly to substrate and metal layers

- Drain and source: cap from metal routing path to substrate and other metal layers

- Resistance

- Gate: poly gate has resistance (reduced by silicide)

- Drain and source: some resistance in diffusion region, and from routing long metal lines

- Inductance

- Gate: poly gate has negligible inductance

- Drain and source: becoming an issue for long wires

**Extract these parasitics from circuit layout**

#### Frequency Performance of a CMOS Device

- Two figures of merit in common use

- **T** f₁: frequency for which current gain is unity

- **■** f<sub>max</sub>: frequency for which power gain is unity

- Common intuition about f,

- Gain, bandwidth product is conserved

- $\Rightarrow$  Gain · Bandwidth =  $f_t$

- We will see that MOS devices have an f<sub>t</sub> that shifts with bias

- This effect strongly impacts high speed amplifier topology selection

- We will focus on f<sub>t</sub>

- Look at pages 70-72 of Tom Lee's book for discussion on f<sub>max</sub>

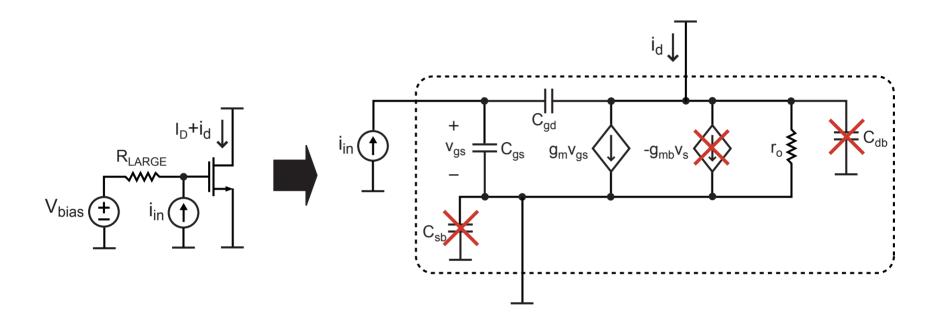

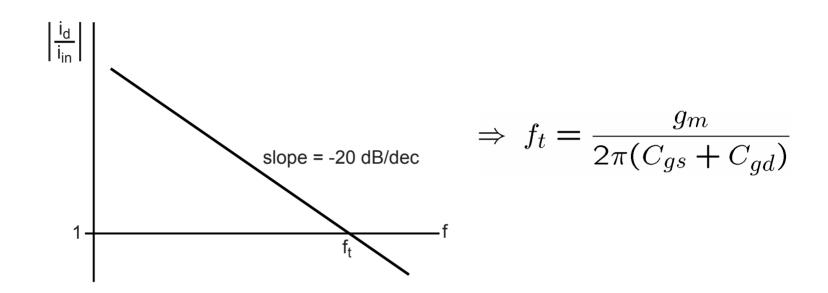

#### Derivation of f, for MOS Device in Saturation

- Assumption is that input is current, output of device is short circuited to a supply voltage

- Note that voltage bias is required at gate

- The calculated value of f<sub>t</sub> is a function of this bias voltage

#### Derivation of f<sub>t</sub> for MOS Device in Saturation

$$i_d = g_m v_{gs} = g_m \left( \frac{1}{s(C_{gs} + C_{gd})} \right) i_{in}$$

$$\Rightarrow \frac{i_d}{i_{in}} = \frac{g_m}{i_{2\pi} f(C_{gs} + C_{gd})}$$

## Derivation of f, for MOS Device in Saturation

$$i_d = g_m v_{gs} = g_m \left( \frac{1}{s(C_{gs} + C_{gd})} \right) i_{in}$$

$$\Rightarrow \frac{i_d}{i_{in}} = \frac{g_m}{j2\pi f(C_{gs} + C_{gd})}$$

#### Why is f<sub>t</sub> a Function of Voltage Bias?

$$f_t = \frac{g_m}{2\pi(C_{gs} + C_{gd})}$$

- f<sub>t</sub> is a ratio of g<sub>m</sub> to gate capacitance

- g<sub>m</sub> is a function of gate bias, while gate cap is not (so long as device remains biased)

- First order relationship between g<sub>m</sub> and gate bias:

$$g_m \approx \mu_n C_{ox} \frac{W}{L} (V_{gs} - V_t)$$

- The larger the gate bias, the higher the value for f<sub>t</sub>

- Alternately, f, is a function of current density

$$\frac{g_m}{C_{gs} + C_{gd}} \approx \frac{\sqrt{2\mu_n C_{ox}(W/L)I_d}}{(2/3)WLC_{ox} + W(C_{ov}/W)} \propto \sqrt{\frac{I_d}{W}}$$

So f₁ maximized at max current density (and minimum L)

#### Speed of NMOS Versus PMOS Devices

$$f_t = \frac{g_m}{2\pi(C_{gs} + C_{gd})}$$

NMOS devices have much higher mobility than PMOS devices (in current, non-strained, bulk CMOS processes)

$$\mu_n \approx 2.5 \mu_p$$

for many processes  $\Rightarrow f_t \text{ of NMOS} \approx 2.5 \times f_t \text{ of PMOS}$

- Intuition: NMOS devices provide approximately 2.5 x g<sub>m</sub> for a given amount of capacitance and gate bias voltage

- Also: NMOS devices provide approximately 2.5 x I<sub>d</sub> for a given amount of capacitance and gate bias voltage

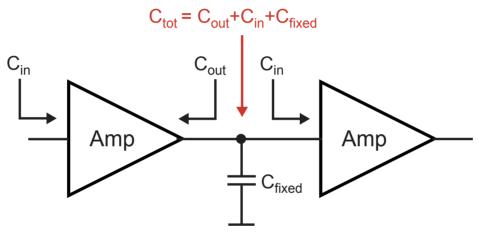

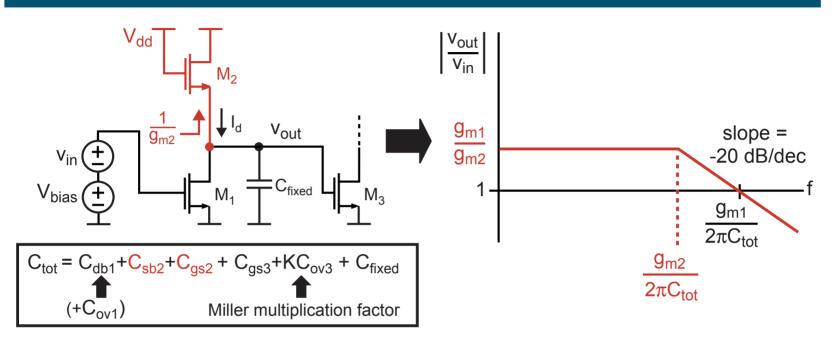

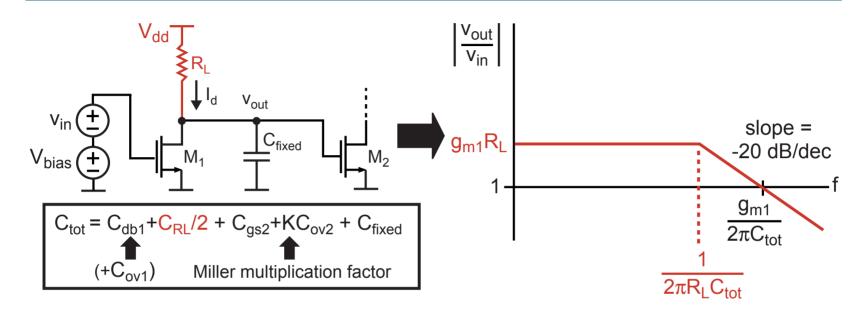

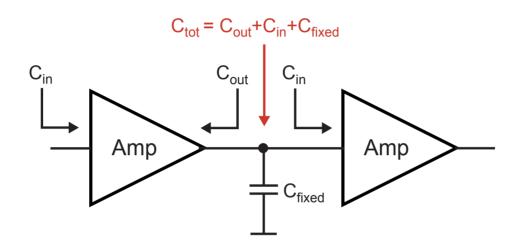

#### Assumptions for High Speed Amplifier Analysis

Assume that amplifier is loaded by an identical amplifier and by fixed wiring capacitance

- Intrinsic performance

- Defined as the bandwidth achieved for a given gain when C<sub>fixed</sub> is negligible

- Amplifier approaches intrinsic performance as its device sizes (and current) are increased

- In practice, optimal sizing (and power) of amplifier is roughly where C<sub>in</sub>+C<sub>out</sub> = C<sub>fixed</sub>

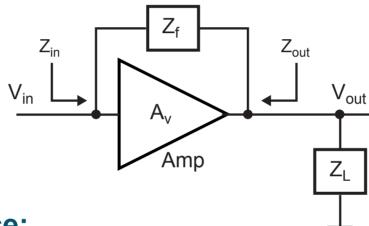

#### The Miller Effect

Concerns impedances that connect from input to output of an amplifier

Input impedance:

$$Z_{in} = \frac{V_{in}}{(V_{in} - V_{out})/Z_f} = \frac{Z_f}{1 - A_v}$$

Output impedance:

$$Z_{out} = rac{V_{out}}{(V_{out} - V_{in})/Z_f} = rac{Z_f}{1 - 1/A_v} pprox Z_f ext{ for } |A_v| \gg 1$$

M.H. Perrott

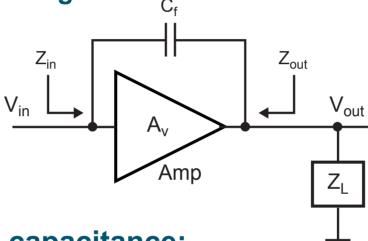

#### Example: The Impact of Capacitance in Feedback

Consider C<sub>ad</sub> in the MOS device as C<sub>f</sub>

Impact on input capacitance:

$$Z_{in} = \frac{1/(sC_f)}{1+|A_v|} = \frac{1}{sC_f(1+|A_v|)} \Rightarrow \text{looks like larger cap!}$$

Output impedance:

$$Z_{out} = \frac{1/(sC_f)}{1+1/|A_v|} = \frac{1}{sC_f(1+1/|A_v|)} \Rightarrow \text{ only slightly larger!}$$

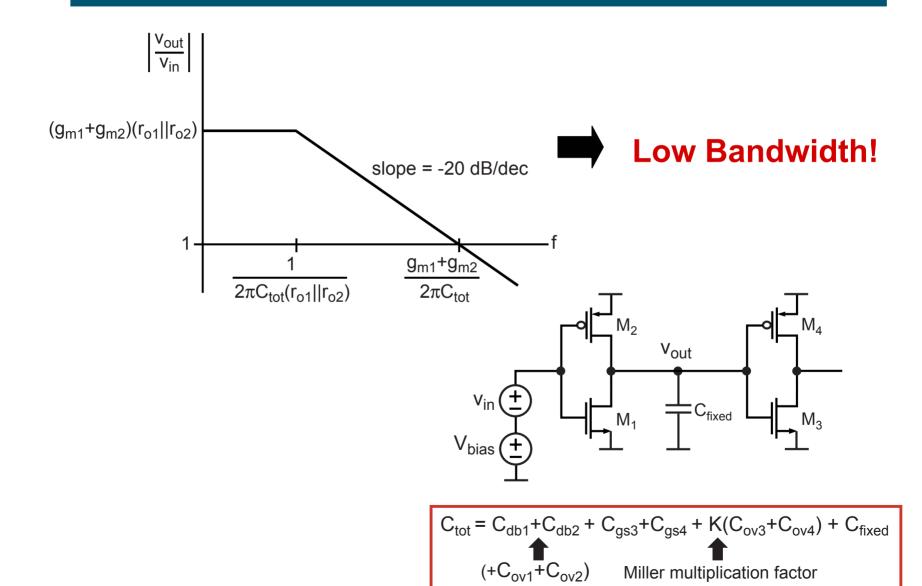

#### Amplifier Example – CMOS Inverter

- Assume that we set V<sub>bias</sub> such that the amplifier nominal output is such that NMOS and PMOS transistors are all in saturation

- Note: this topology VERY sensitive to bias errors

#### Transfer Function of CMOS Inverter

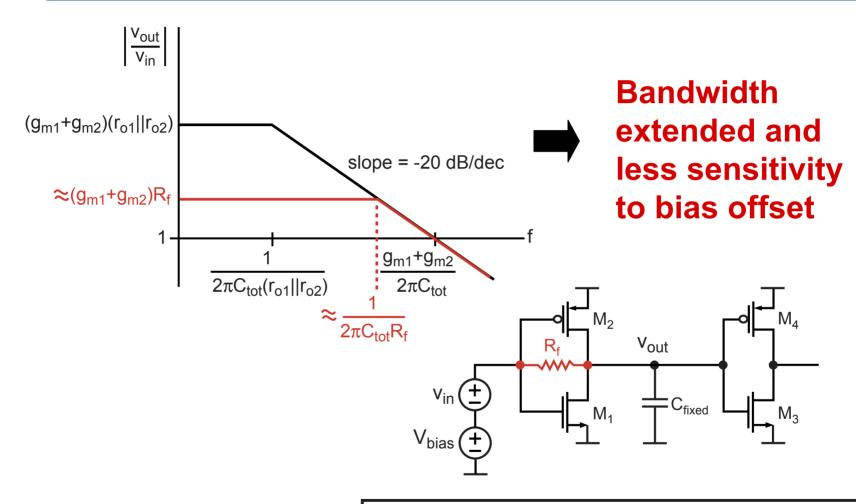

#### Add Resistive Feedback

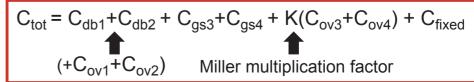

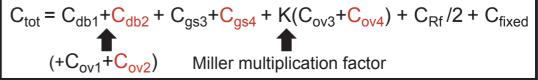

$$C_{\text{tot}} = C_{\text{db1}} + C_{\text{db2}} + C_{\text{gs3}} + C_{\text{gs4}} + K(C_{\text{ov3}} + C_{\text{ov4}}) + \frac{C_{\text{Rf}}}{2} + C_{\text{fixed}}$$

$$(+C_{\text{ov1}} + C_{\text{ov2}}) \qquad \text{Miller multiplication factor}$$

#### We Can Still Do Better

- We are fundamentally looking for high g<sub>m</sub> to capacitance ratio to get the highest bandwidth

- PMOS degrades this ratio

- Gate bias voltage is constrained

M.H. Perrott

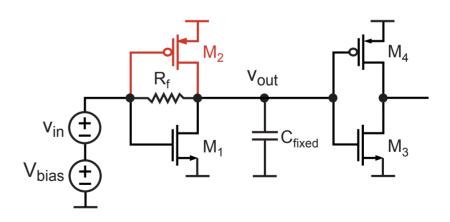

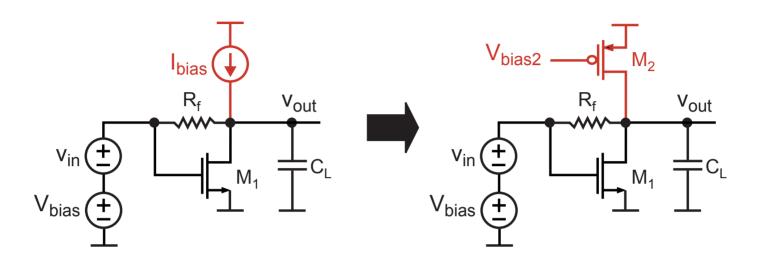

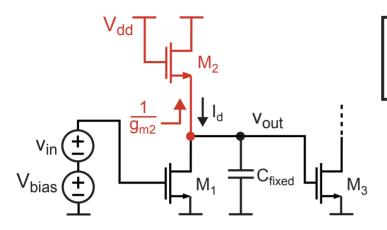

#### Take PMOS Out of the Signal Path

- Advantages

- PMOS gate no longer loads the signal

- NMOS device can be biased at a higher voltage

- Issue

- PMOS is not an efficient current provider (I<sub>d</sub>/drain cap)

- Drain cap close in value to C<sub>qs</sub>

- Signal path is loaded by cap of R<sub>f</sub> and drain cap of PMOS

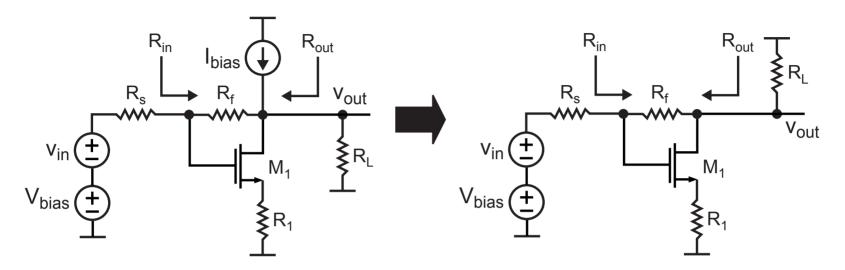

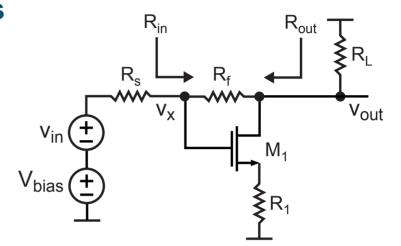

#### **Shunt-Series Amplifier**

- Use resistors to control the bias, gain, and input/output impedances

- Improves accuracy over process and temp variations

- Issues

- Degeneration of M<sub>1</sub> lowers slew rate for large signal applications (such as limit amps)

- There are better high speed approaches the advantage of this one is simply accuracy

## Shunt-Series Amplifier – Analysis Snapshot

## From Chapter 8 of Tom Lee's book (see pp 191-197):

Gain

$$A_v = \frac{v_{out}}{v_{in}} = -\frac{R_L}{R_E} \left( \frac{R_f - R_E}{R_f + R_L} \right) \quad \text{v}_{\text{in}} \stackrel{\text{t}}{\rightleftharpoons} \quad \text{where:} \quad R_E = 1/g_m + R_1$$

Note:  $A_v \approx -\frac{R_L}{R_1}$  for  $R_f \gg R_L, \ R_f \gg R_E, \ R_1 \gg 1/g_m$

Input resistance

$$R_{in} = \frac{R_f}{1 - A_v} = \frac{R_E(R_f + R_L)}{R_E + R_L} \approx \frac{R_f}{1 + R_L/R_1} \quad \text{for } R_f \gg R_L, \\ R_1 \gg 1/g_m$$

**Output resistance**

Output resistance

$$R_{out} = \frac{R_E(R_f + R_s)}{R_E + R_s} \approx \frac{R_f}{1 + R_s/R_1} \quad \text{for } R_f \gg R_s, R_1 \gg 1/g_m$$

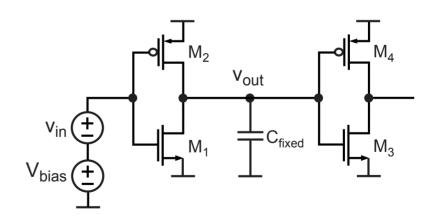

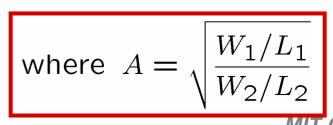

#### NMOS Load Amplifier

## Gain set by the relative sizing of M₁ and M₂

$$M_1: I_{d1} = (1/2)\mu_n C_{ox}(W_1/L_1)(V_{IN} - V_T)^2$$

$$M_2: I_{d2} = (1/2)\mu_n C_{ox}(W_2/L_2)(V_{dd}-V_{out}-V_T)^2$$

$$I_{d1} = I_{d2}$$

$$\Rightarrow V_{out} = -AV_{IN} + V_{dd} + (A-1)V_T \ (V_{IN} = V_{in} + V_{bias})$$

where  $A = \sqrt{1}$

M.H. Perrott

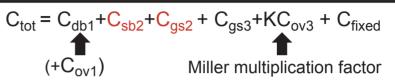

#### Design of NMOS Load Amplifier

$$A = \sqrt{\frac{W_1/L_1}{W_2/L_2}}$$

- Size transistors for gain and speed

- Choose minimum L for maximum speed

- Choose ratio of W<sub>1</sub> to W<sub>2</sub> to achieve appropriate gain

- Problem: V<sub>T</sub> of M<sub>2</sub> lowers the bias voltage of the next stage (thus lowering its achievable f₁)

- Severely hampers performance when amplifier is cascaded

- One person solved this issue by increasing V<sub>dd</sub> of NMOS load (see Sackinger et. al., "A 3-GHz 32-dB CMOS Limiting Amplifier for SONET OC-48 receivers", JSSC, Dec 2000)

M.H. Perrott

#### Resistor Loaded Amplifier (Unsilicided Poly)

- This is the fastest non-enhanced amplifier I've found

- Unsilicided poly is a pretty efficient current provider (i..e, has a good current to capacitance ratio)

- Output swing can go all the way up to V<sub>dd</sub>

- Allows following stage to achieve high f<sub>t</sub>

- Linear settling behavior (in contrast to NMOS load)

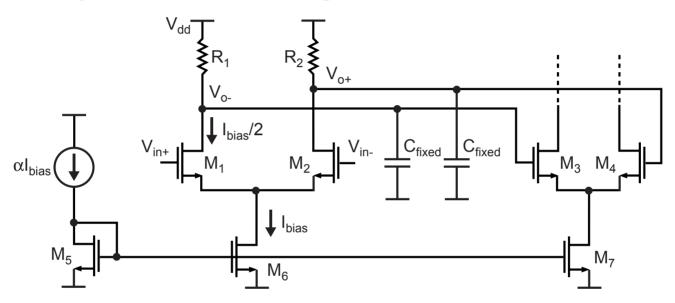

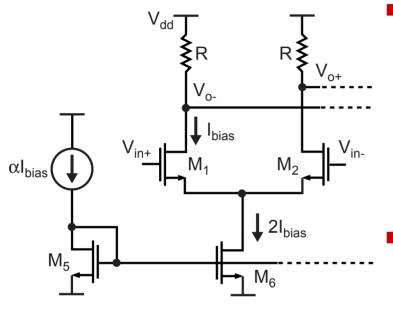

#### Implementation of Resistor Loaded Amplifier

Typically implement using differential pairs

- Benefits

- Self-biased

- Common-mode rejection

- Negative

- More power than single-ended version

#### The Issue of Velocity Saturation

We classically assume that MOS current is calculated as

$$I_D = \frac{\mu_n C_{ox} W}{2} (V_{gs} - V_T)^2$$

Which is really

$$I_D = \frac{\mu_n C_{ox} W}{2} (V_{gs} - V_T) V_{dsat,l}$$

- $ightharpoonup V_{dsat,l}$  corresponds to the saturation voltage at a given length, which we often refer to as  $\Delta V$

- It may be shown that

$$V_{dsat,l} \approx \frac{(V_{gs} - V_T)(LE_{sat})}{(V_{gs} - V_T) + (LE_{sat})} = (V_{gs} - V_T)||(LE_{sat})|$$

- If V<sub>gs</sub>-V<sub>T</sub> approaches LE<sub>sat</sub> in value, then the top equation is no longer valid

- We say that the device is in velocity saturation

#### Analytical Device Modeling in Velocity Saturation

If L small (as in modern devices), than velocity saturation will impact us for even moderate values of V<sub>gs</sub>-V<sub>T</sub>

$$I_D = \frac{\mu_n C_{ox} W}{2} [(V_{gs} - V_T)[(V_{gs} - V_T)||(LE_{sat})]$$

$$\Rightarrow I_D pprox rac{\mu_n C_{ox}}{2} W(V_{gs} - V_T) E_{sat}$$

- Current increases linearly with V<sub>gs</sub>-V<sub>T</sub>!

- Transconductance in velocity saturation:

$$g_m = \frac{dI_d}{dV_{gs}} \Rightarrow g_m = \frac{\mu_n C_{ox}}{2} W E_{sat}$$

No longer a function of V<sub>qs</sub>!

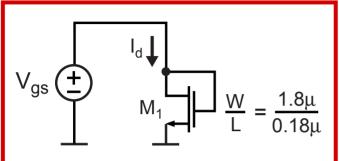

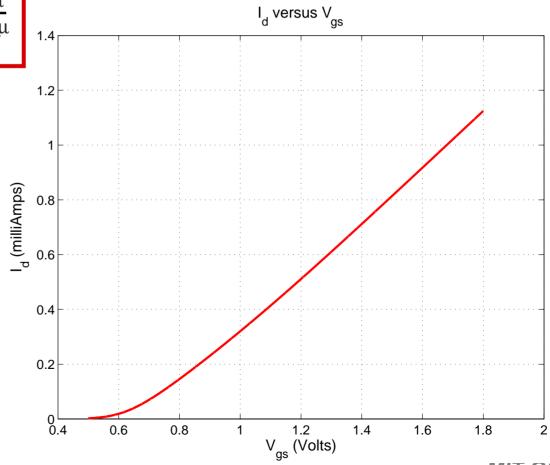

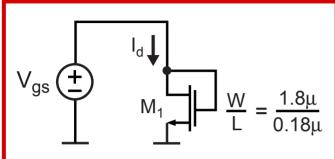

# Example: Current Versus Voltage for 0.18 µ Device

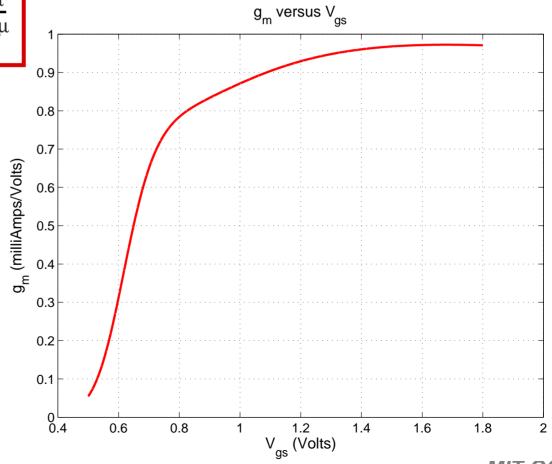

# Example: $G_m$ Versus Voltage for $0.18\mu$ Device

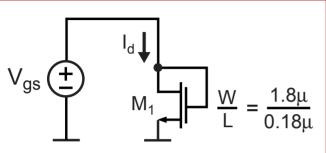

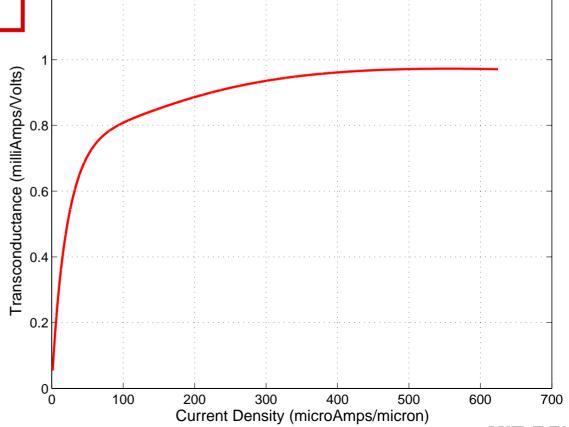

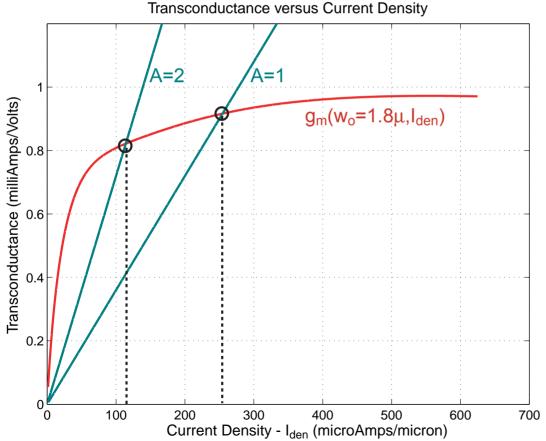

# Example: G<sub>m</sub> Versus Current Density for 0.18 µ Device

Note:

$$I_{den} = \frac{I_d}{W} = \frac{I_d}{1.8\mu}$$

Transconductance versus Current Density

#### How Do We Design the Amplifier?

- Highly inaccurate to assume square law behavior

- We will now introduce a numerical procedure based on the simulated g<sub>m</sub> curve of a transistor

- A look at g<sub>m</sub> assuming square law device:

$$g_m = \sqrt{2\mu C_{ox} \frac{W}{L} I_d} = W \sqrt{2\mu C_{ox} \frac{W}{L} \left(\frac{I_d}{W}\right)}$$

- Observe that if we keep the current density (I<sub>d</sub>/W) constant, then g<sub>m</sub> scales directly with W

- This turns out to be true outside the square-law regime as well

- We can therefore relate g<sub>m</sub> of devices with different widths given that have the same current density

$$g_m(W, I_{den}) = \frac{W}{W_o} g_m(W_o, I_{den})$$

# A Numerical Design Procedure for Resistor Amp – Step 1

- Two key equations

- Set gain and swing (singleended)

$$(1) g_m(W, I_{bias}/W)R = A$$

$$(2) V_{sw} = 2I_{bias}R$$

Equate (1) and (2) through R

$$\frac{A}{g_m(W, I_{bias}/W)} = \frac{V_{sw}}{2I_{bias}}$$

$$\Rightarrow g_m(W, I_{bias}/W) = 2\frac{A}{V_{sw}}W\left(\frac{I_{bias}}{W}\right)$$

Can we relate this formula to a g<sub>m</sub> curve taken from a device of width W<sub>o</sub>?

## A Numerical Design Procedure for Resistor Amp – Step 2

We now know:

(1)

$$g_m(W, I_{bias}/W) = 2\frac{A}{V_{sw}}W\left(\frac{I_{bias}}{W}\right)$$

(2)  $g_m(W, I_{den}) = \frac{W}{W_o}g_m(W_o, I_{den})$

Substitute (2) into (1)

$$\frac{W}{W_o}g_m(W_o, I_{bias}/W) = 2\frac{A}{V_{sw}}W\left(\frac{I_{bias}}{W}\right)$$

$$\Rightarrow g_m(W_o, I_{den}) = 2W_o \frac{A}{V_{sw}} I_{den}$$

■ The above expression allows us to design the resistor loaded amp based on the g<sub>m</sub> curve of a representative transistor of width W<sub>o</sub>!

## Example: Design for Swing of 1 V, Gain of 1 and 2

$$g_m(W_o, I_{den}) = 2W_o \frac{A}{V_{sw}} I_{den}$$

Assume L=0.18μ, use previous g<sub>m</sub> plot (W<sub>o</sub>=1.8μ)

- For gain of 1,current density =250 μA/μm

- For gain of 2,current density =115 μΑ/μm

- Note that current density reduced as gain increases!

- f<sub>t</sub> effectively decreased

#### Example (Continued)

- Knowledge of the current density allows us to design the amplifier

- Recall  $V_{sw} = 2I_{bias}R$

- **■** Free parameters are W, I<sub>bias</sub>, and R (L assumed to be fixed)

- Given  $I_{den} = 115 \,\mu\text{A}/\mu\text{m}$  (Swing = 1V, Gain = 2)

- If we choose  $I_{bias} = 300 \mu A$

$$I_{den} = \frac{I_{bias}}{W} \Rightarrow W = \frac{300}{115} = 2.6 \mu m$$

$V_{sw} = 2I_{bias}R \Rightarrow R = \frac{1}{2 \cdot 300 \times 10^{-6}} = 1.67 k\Omega$

Note that we could instead choose W or R, and then calculate the other parameters

M.H. Perrott MIT

# How Do We Choose I<sub>bias</sub> For High Bandwidth?

- As you increase I<sub>bias</sub>, the size of transistors also increases to keep a constant current density

- The size of C<sub>in</sub> and C<sub>out</sub> increases relative to C<sub>fixed</sub>

- To achieve high bandwidth, want to size the devices (i.e., choose the value for I<sub>bias</sub>), such that

- C<sub>in</sub>+C<sub>out</sub> roughly equal to C<sub>fixed</sub>