#### 6.012 - Microelectronic Devices and Circuits

## Lecture 16 - CMOS scaling; The Roadmap - Outline

#### Announcements

PS #9 - Will be due next week Friday; no recitation tomorrow.

**Postings - CMOS scaling (multiple items)**

**Exam Two - Tonight, Nov. 5, 7:30-9:30 pm**

## • Review - CMOS gate delay and power

**Lecture 15 results:** Gate Delay = 12 n  $L_{min}^2 V_{DD} / \mu_n (V_{DD} - V_T)^2$  $P_{dvn}@f_{max} \propto C_L V_{DD}^2 / GD = K_n V_{DD} (V_{DD} - V_T)^2 / 4$

**Velocity Saturation**

## CMOS scaling rules

Power density issues and challenges

Approaches to a solution: Dimension scaling alone

Scaling voltages as well

## The Road Map; the Future

Size and performance evolution with time How long can it go on?

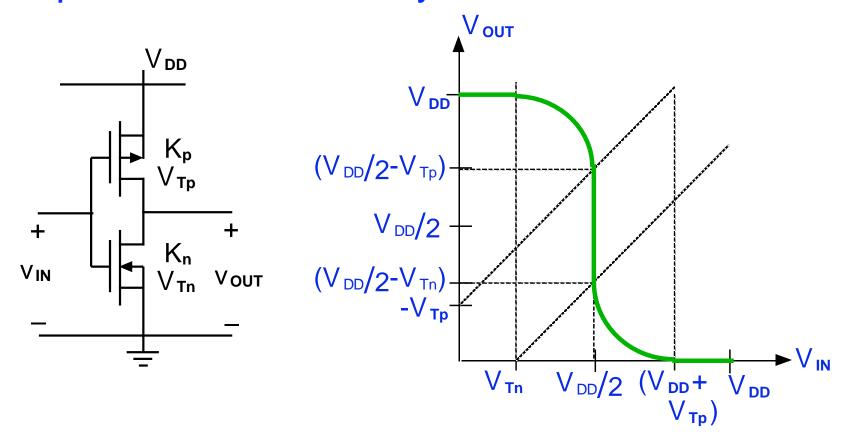

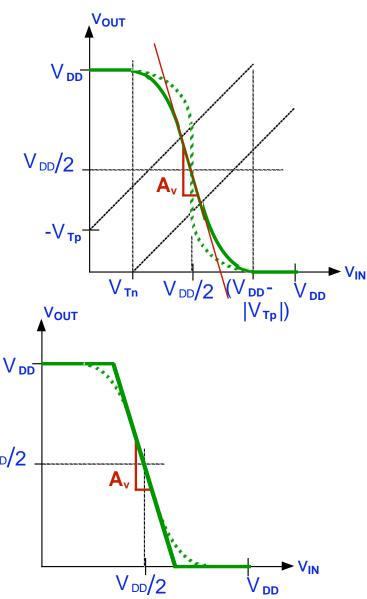

## **CMOS**: transfer characteristic

### Complete characteristic w.o. Early effect:

**NOTE:** We design CMOS inverters to have  $K_n = K_p$  and  $V_{Tn} = -V_{Tp}$  to obtain the optimum symmetrical characteristic.

## **CMOS**: transfer characteristic calculation, cont.

We found from an LEC analysis that the slope in Region III is not infinite, but is instead:

$$A_{v} = \frac{v_{out}}{v_{in}} = \frac{\partial v_{OUT}}{\partial v_{IN}} \bigg|_{Q(=V_{DD}/2, V_{DD}/2)}$$

$$= -\frac{\left[g_{mn} + g_{mp}\right]}{\left[g_{on} + g_{op}\right]} = -\frac{2\sqrt{2K_{n}}}{\left[\lambda_{n} + \lambda_{p}\right]\sqrt{I_{Dn}}}$$

Quick approximation: An easy way to sketch the transfer characteristic of a CMOS gate is to simply draw the three straight line portions in Regions I, III, and V:

Lecture 16 - Slide 3

Clif Fonstad, 11/5/09

## **CMOS**: switching speed; minimum cycle time

## The load capacitance: C<sub>L</sub>

- Assume to be linear

- Is proportional to MOSFET gate area

- In channel:  $\mu_e = 2\mu_h$  so to have  $K_n = K_p$  we must have  $W_p/L_p = 2W_n/L_n$ Typically  $L_n = L_p = L_{min}$  and  $W_n = W_{min}$ , so we also have  $W_p = 2W_{min}$

$$C_L \approx n [W_n L_n + W_p L_p] C_{ox}^* = n [W_{\min} L_{\min} + 2W_{\min} L_{\min}] C_{ox}^* = 3n W_{\min} L_{\min} C_{ox}^*$$

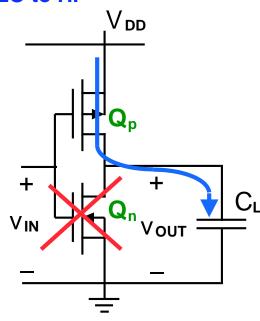

## **Charging cycle:** $v_{IN}$ : HI to LO; $Q_n$ off, $Q_p$ on; $v_{OUT}$ : LO to HI

Assume charged by constant i<sub>D,sat</sub>

$$i_{Ch \text{ arg } e} = -i_{Dp} \approx \frac{K_p}{2} [V_{DD} - |V_{Tp}|]^2 = \frac{K_n}{2} [V_{DD} - V_{Tn}]^2$$

$$q_{Ch \arg e} = C_L V_{DD}$$

$$\tau_{Ch \, \text{arg} \, e} = \frac{q_{Ch \, \text{arg} \, e}}{i_{Ch \, \text{arg} \, e}} = \frac{2C_L V_{DD}}{K_n [V_{DD} - V_{Tn}]^2}$$

$$= \frac{6nW_{\min}L_{\min}C_{ox}^{*}V_{DD}}{\frac{W_{\min}}{I}\mu_{e}C_{ox}^{*}[V_{DD}-V_{Tn}]^{2}} = \frac{6nL_{\min}^{2}V_{DD}}{\mu_{e}[V_{DD}-V_{Tn}]^{2}}$$

Lecture 16 - Slide 4

Clif Fonstad, 11/5/09

## **CMOS**: switching speed; minimum cycle time, cont.

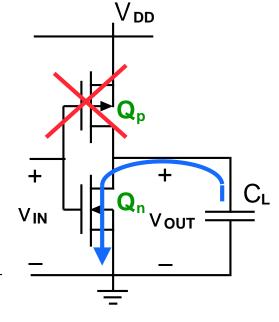

## **<u>Discharging cycle</u>**: $v_{IN}$ : LO to HI; $Q_n$ on, $Q_p$ off; $v_{OUT}$ : HI to LO

Assume discharged by constant i<sub>D,sat</sub>

$$i_{Disch \arg e} = i_{Dn} \approx \frac{K_n}{2} [V_{DD} - V_{Tn}]^2$$

$$q_{Disch\,arg\,e} = C_L V_{DD}$$

$$\tau_{Disch \arg e} = \frac{q_{Disch \arg e}}{i_{Disch \arg e}} = \frac{2C_L V_{DD}}{K_n [V_{DD} - V_{Tn}]^2}$$

$$= \frac{6nW_{\min}L_{\min}C_{ox}^{*}V_{DD}}{\frac{W_{\min}}{L}\mu_{e}C_{ox}^{*}[V_{DD}-V_{Tn}]^{2}} = \frac{6nL_{\min}^{2}V_{DD}}{\mu_{e}[V_{DD}-V_{Tn}]^{2}}$$

<u>Minimum cycle time</u>:  $v_{IN}$ : LO to HI to LO;  $v_{OUT}$ : HI to LO to HI

$$\tau_{Min.Cycle} = \tau_{Ch \operatorname{arg} e} + \tau_{Disch \operatorname{arg} e} = \frac{12nL_{\min}^2 V_{DD}}{\mu_e [V_{DD} - V_{Tn}]^2}$$

## **CMOS**: switching speed; minimum cycle time, cont.

### **Discharging and Charging times:**

What do the expressions tell us? We have

$$\tau_{Min\,Cycle} = \frac{12nL_{\min}^2 V_{DD}}{\mu_e \left[V_{DD} - V_{Tn}\right]^2}$$

This can be written as:

$$\tau_{Min\,Cycle} = \frac{12nV_{DD}}{\left(V_{DD} - V_{Tn}\right)} \cdot \frac{L_{\min}}{\mu_e \left(V_{DD} - V_{Tn}\right)/L_{\min}}$$

The last term is the channel transit time:

$$\frac{L_{\min}}{\mu_e \left(V_{DD} - V_{Tn}\right)/L_{\min}} = \frac{L_{\min}}{\mu_e E_{Ch}} = \frac{L_{\min}}{\overline{s}_{e,Ch}} = \tau_{Ch Transit}$$

Thus the gate delay is a multiple of the channel transit time:

$$\tau_{Min\,Cycle} = \frac{12nV_{DD}}{\left(V_{DD} - V_{Tn}\right)} \tau_{Channel\,Transit} = n' \tau_{Channel\,Transit}$$

## **CMOS**: power dissipation - total and per unit area

#### **Average power dissipation**

Only dynamic for now

$$P_{dyn,ave} = E_{Dissipated\ per\ cycle} f = C_L V_{DD}^2 = 3nW_{\min} L_{\min} C_{ox}^* V_{DD}^2 f$$

#### Power at maximum data rate

Maximum f will be  $1/\tau_{\text{Gate Delay Min.}}$

$$P_{dyn@f_{\text{max}}} = \frac{3nW_{\text{min}}L_{\text{min}}C_{ox}^{*}V_{DD}^{2}}{\tau_{Min.Cycle}} = 3nW_{\text{min}}L_{\text{min}}C_{ox}^{*}V_{DD}^{2} \cdot \frac{\mu_{e}[V_{DD} - V_{Tn}]^{2}}{12nL_{\text{min}}^{2}V_{DD}}$$

$$= \frac{1}{4}\frac{W_{\text{min}}}{L_{\text{min}}}\mu_{e}C_{ox}^{*}V_{DD}[V_{DD} - V_{Tn}]^{2}$$

#### Power density at maximum data rate

Assume that the area per inverter is proportional to  $W_{\min}L_{\min}$

$$PD_{dyn@f_{\text{max}}} = \frac{P_{dyn@f_{\text{max}}}}{\text{InverterArea}} \propto \frac{P_{dyn@f_{\text{max}}}}{W_{\text{min}}L_{\text{min}}} = \frac{\mu_e C_{ox}^* V_{DD} [V_{DD} - V_{Tn}]^2}{L_{\text{min}}^2}$$

## **CMOS**: design for high speed

#### **Maximum data rate**

Proportional to  $1/\tau_{Min\ Cycle}$

$$\tau_{Min.Cycle} = \tau_{Ch \text{ arg } e} + \tau_{Disch \text{ arg } e} = \frac{12nL_{\min}^2 V_{DD}}{\mu_e \left[V_{DD} - V_{Tn}\right]^2}$$

## Implies we should reduce $L_{min}$ and increase $V_{DD}$ .

**Note:** As we reduce  $L_{min}$  we must also reduce  $t_{ox}$ , but  $t_{ox}$  doesn't enter directly in  $f_{max}$  so it doesn't impact us here

#### Power density at maximum data rate

Assume that the area per inverter is proportional to W<sub>min</sub>L<sub>min</sub>

$$PD_{dyn @ f_{\text{max}}} \propto \frac{P_{dyn @ f_{\text{max}}}}{W_{\text{min}} L_{\text{min}}} = \frac{\mu_e \varepsilon_{ox} V_{DD} [V_{DD} - V_{Tn}]^2}{t_{ox} L_{\text{min}}^2}$$

Shows us that PD increases very quickly as we reduce  $L_{min}$  unless we also reduce  $V_{DD}$  (which will also reduce  $f_{max}$ ).

**Note:** Now t<sub>ox</sub> does appear in the expression, so the rate of increase with decreasing L<sub>min</sub> is even greater because t<sub>ox</sub> must be reduced along with L to stay in the gradual channel regime.

How do we make f<sub>max</sub> larger without melting the silicon?

Clif Fonstad, 11/5/09 By following CMOS scaling rules, the topic of today's lecture. Lecture 16 - Slide 8

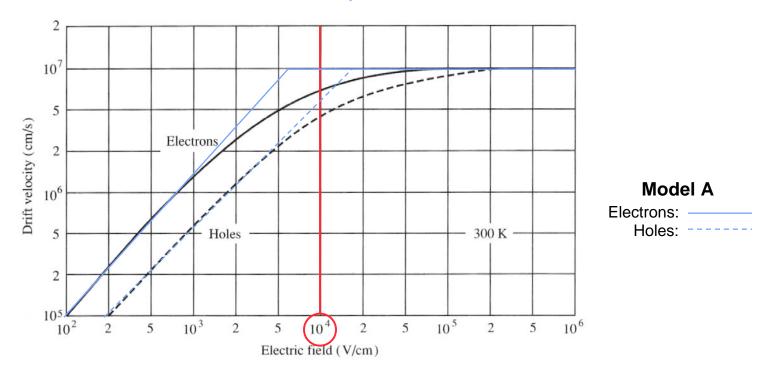

## **CMOS**: velocity saturation

#### Sanity check before looking at device scaling

CMOS gate lengths are now under 0.1  $\mu m$  (100 nm). The electric field in the channel can be very high:  $E_v \ge 10^4$  V/cm when  $v_{DS} \ge 0.1$  V.

Clearly the velocity of the electrons and holes in the channel will be saturated at even low values of  $v_{DS}!$

What does this mean for the device and inverter characteristics?

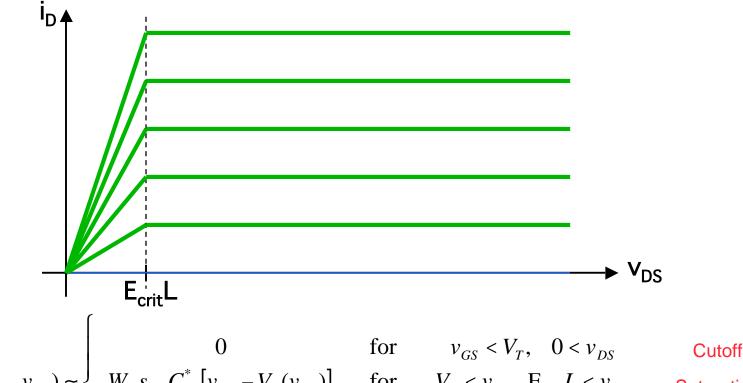

## **MOS**: Output family with velocity saturation

$$i_{D}(v_{GS}, v_{DS}, v_{BS}) \approx \begin{cases} 0 & \text{for} \quad v_{GS} < V_{T}, \quad 0 < v_{DS} \\ W \ s_{sat} \ C_{ox}^{*} \left[ v_{GS} - V_{T}(v_{BS}) \right] & \text{for} \quad V_{T} < v_{GS}, \quad \mathbf{E}_{crit} L < v_{DS} \\ \frac{W}{L} \ \mu_{e} \ C_{ox}^{*} \left[ v_{GS} - V_{T}(v_{BS}) \right] v_{DS} & \text{for} \quad V_{T} < v_{GS}, \quad 0 < v_{DS} < \mathbf{E}_{crit} L \end{cases}$$

Linear

This simple model for the <u>output characteristics</u> of a very short channel MOSFET (plotted above) provides us an easy way to understand the impact of velocity saturation on MOSFET and CMOS inverter performance.

## **CMOS**: Gate delay and f<sub>max</sub> with velocity saturation

### Charge/discharge cycle and gate delay:

The charge and discharge currents, charges, and times are now:

$$\begin{split} i_{Disch \, \text{arg} \, e} &= i_{Ch \, \text{arg} \, e} = W_{\min} \, s_{sat} \, C_{ox}^* \left( V_{DD} - V_{Tn} \right) \\ q_{Disch \, \text{arg} \, e} &= q_{Ch \, \text{arg} \, e} = C_L V_{DD} = 3 W_{\min} L_{\min} C_{ox}^* V_{DD} \\ \tau_{Disch \, \text{arg} \, e} &= \tau_{Ch \, \text{arg} \, e} = \frac{q_{Disch \, \text{arg} \, e}}{i_{Disch \, \text{arg} \, e}} = \frac{3 W_{\min} L_{\min} C_{ox}^* V_{DD}}{W_{\min} \, s_{sat} \, C_{ox}^* \left( V_{DD} - V_{Tn} \right)} = \frac{3n L_{\min} V_{DD}}{s_{sat} \left( V_{DD} - V_{Tn} \right)} \end{split}$$

### CMOS minimum cycle time and power density at $f_{max}$ :

$$au_{Min.Cycle} = au_{Ch \, arg \, e} + au_{Disch \, arg \, e} = rac{6 \, n \, L_{\min} V_{DD}}{s_{sat} \left[ V_{DD} - V_{Tn}

ight]}$$

Note:  $au_{ChanTransit} = rac{L}{s_{sat}}$

$$\tau_{Min.Cycle} \propto \frac{L_{min}V_{DD}}{s_{sat}[V_{DD} - V_{Tn}]} = n'\tau_{ChanTransit}$$

Lessons: We still benefit from reducing L, but not as quickly. Channel transit time,  $L_{min}/s_{sat}$ , is still critical.

## **CMOS**: Power and power density with velocity saturation

### **Average power dissipation**

**All dynamic**

$$P_{ave} = E_{Dissipated\ per\ cycle} f = C_L V_{DD}^2 = 3nW_{min} L_{min} C_{ox}^* V_{DD}^2 f$$

#### Power at maximum data rate

Maximum f will be 1/τ<sub>Gate Delay Min.</sub>

$$P_{dyn @ f_{\text{max}}} = \frac{3nW_{\text{min}}L_{\text{min}}C_{ox}^{*}V_{DD}^{2}}{\tau_{Min.Cycle}} = 3nW_{\text{min}}L_{\text{min}}C_{ox}^{*}V_{DD}^{2} \cdot \frac{s_{sat}[V_{DD} - V_{Tn}]}{6nL_{\text{min}}V_{DD}}$$

$$= \frac{1}{2}W_{\text{min}}s_{sat}C_{ox}^{*}V_{DD}[V_{DD} - V_{Tn}]$$

#### Power density at maximum data rate

Assume that the area per inverter is proportional to  $W_{\min}L_{\min}$

$$PD_{dyn@f_{max}} = \frac{P_{dyn@f_{max}}}{InverterArea} \propto \frac{P_{dyn@f_{max}}}{W_{min}L_{min}} = \frac{s_{sat} C_{ox}^* V_{DD}[V_{DD} - V_{Tn}]}{L_{min}}$$

Lesson: Again benefit from reducing L, but again not as quickly.

## **CMOS:** Collected results

#### **Maximum data rate:**

No velocity saturation:

$$\tau_{Min.Cycle} \propto \frac{L_{\min}^2 V_{DD}}{\mu_e \big[ V_{DD} - V_{Tn} \big]^2}$$

on:

$$\tau_{Min.Cycle} \propto \frac{L_{\min} V_{DD}}{s_{sat} \big[ V_{DD} - V_{Tn} \big]}$$

Smaller is faster

With velocity saturation:

$$au_{Min.Cycle} \propto rac{L_{\min} V_{DD}}{s_{sat} [V_{DD} - V_{Tn}]}$$

### **Power density at maximum data rate:**

No velocity saturation:

PD<sub>dyn @ f<sub>max</sub></sub> =

$$\frac{\mu_e \, \varepsilon_{ox} \, V_{DD} \big[ V_{DD} - V_{Tn} \big]^2}{t_{ox} \, L_{\min}^2}$$

Smaller also dissipates more power per unit area

$$PD_{dyn \, @ \, f_{\max}} = \frac{s_{sat} \, \varepsilon_{ox} \, V_{DD} \big[ V_{DD} - V_{Tn} \big]}{t_{ox} \, L_{\min}}$$

With velocity saturation:

$$PD_{dyn @ f_{max}} = \frac{s_{sat} \varepsilon_{ox} V_{DD} [V_{DD} - V_{Tn}]}{t_{ox} L_{min}}$$

## Scaling Rules - making CMOS faster without melting Si

#### **General idea:**

Reduce dimensions by factor 1/s: s > 1

**Evaluate impact on speed, power, power density**

Assume no velocity saturation for now

#### Scaling dimensions alone:

$$L_{\min} \rightarrow L_{\min}/s$$

$W \rightarrow W/s$   $t_{ox} \rightarrow t_{ox}/s$   $N_A \rightarrow sN_A$

#### This yields

$$C_{ox}^* = \frac{\varepsilon_{ox}}{t_{ox}}$$

:  $C_{ox}^* \rightarrow sC_{ox}^*$   $K = \frac{W}{L}\mu_e C_{ox}^*$ :  $K \rightarrow sK$

#### and thus

$$\tau \propto \frac{L_{\min}^2 V_{DD}}{\mu_e \left[ V_{DD} - V_{Tn} \right]^2} : \qquad \tau \to \tau / s^2$$

$$P_{dyn} = 3nW_{\min}L_{\min}C_{ox}^*V_{DD}^2f: \qquad P_{dyn} \rightarrow sP_{dyn}$$

$$PD_{dyn @ f_{\text{max}}} = \frac{\mu_e \, \varepsilon_{ox} \, V_{DD} \left[ V_{DD} - V_{Tn} \right]^2}{t_{ox} \, L_{\min}^2} : \quad PD_{dyn @ f_{\text{max}}} \rightarrow s^3 PD_{dyn @ f_{\text{max}}}$$

## Scaling Rules, cont. - constant E-field scaling

#### **Observation:**

Reducing dimensions alone won't work.

Reduce voltage in concert (constant E-field scaling)

#### Scaling dimensions and voltages by 1/s:

$$L_{\min} \to L_{\min}/s \qquad W \to W/s \qquad t_{ox} \to t_{ox}/s \qquad N_A \to sN_A$$

$$V_{DD} \to V_{DD}/s \qquad V_{BS} \to V_{BS}/s \qquad V_T \to V_T/s$$

We still have

$$C_{ox}^* \rightarrow sC_{ox}^* \qquad K \rightarrow sK$$

but now we find

$$\tau \propto \frac{L_{\min}^{2} V_{DD}}{\mu_{e} [V_{DD} - V_{Tn}]^{2}} : \qquad \tau \rightarrow \tau / s$$

$$P_{dyn} = 3n W_{\min} L_{\min} C_{ox}^{*} V_{DD}^{2} f : \qquad P_{dyn} \rightarrow P_{dyn} / s^{2}$$

$$PD_{dyn @ f_{\max}} = \frac{\mu_{e} \varepsilon_{ox} V_{DD} [V_{DD} - V_{Tn}]^{2}}{t_{\infty} L_{\min}^{2}} : \qquad PD_{dyn @ f_{\max}} \rightarrow PD_{dyn @ f_{\max}} \rightarrow PD_{dyn @ f_{\max}}$$

When we scale dimension and voltage we get higher speed and lower power, while holding the power density unchanged.

## Scaling Rules, cont. - constant E-field scaling

#### Threshold voltage:

We've said  $V_T$  scales, but this merits some discussion\*:

$$\begin{split} V_T(v_{BS}) &\equiv V_{FB} + \left|2\phi_{p-Si}\right| + \frac{t_{ox}}{\varepsilon_{ox}}\sqrt{2\varepsilon_{Si}qN_A\left[\left|2\phi_{p-Si}\right| + \left|v_{BS}\right|\right]} \\ \text{Small because with n+-poly Si} \\ \text{gate, } \phi_\text{m} \approx \text{-} \ \phi_\text{p} \ \text{and} \ V_\text{FB} \approx \text{-}|2\phi_\text{p}| \end{split} \qquad \begin{array}{c} \text{Dominated by } |\mathbf{v}_\text{BS}| \ \text{if } \\ |\mathbf{v}_\text{BS}| >> \ |2\phi_\text{p}| \end{split}$$

Thus:

$$V_{T}(v_{BS}) \approx \frac{t_{ox}}{\varepsilon_{ox}} \sqrt{2\varepsilon_{Si}qN_{A}|v_{BS}|} \rightarrow \frac{t_{ox}/s}{\varepsilon_{ox}} \sqrt{2\varepsilon_{Si}qsN_{A}|v_{BS}|/s} \rightarrow V_{T}/s$$

It works.

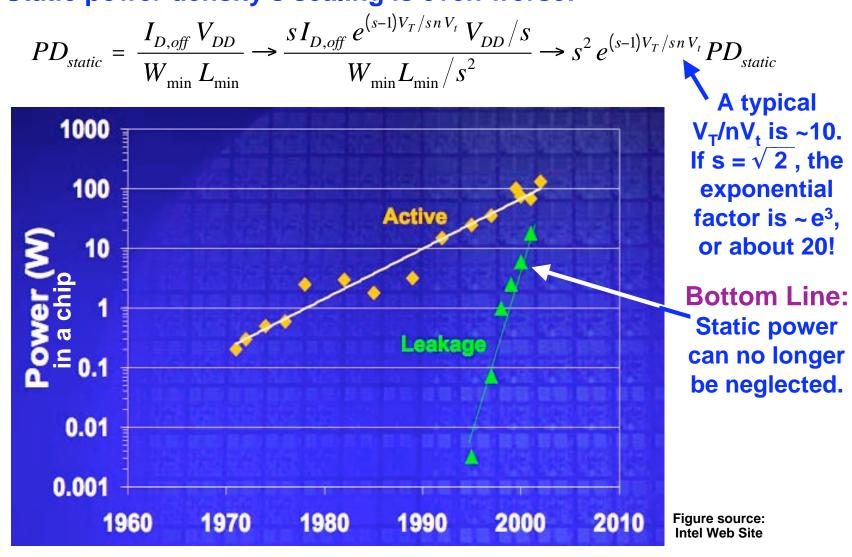

#### Subthreshold leakage and static power:

Including  $V_{BS}$ ,  $I_{Doff}$  is:

$$I_{D,off} \approx \frac{W}{L} \mu_e V_t^2 \sqrt{\frac{\varepsilon_{Si} q N_A}{2[-|2\phi_p| + |V_{BS}|]}} \quad e^{\{-V_T\}/nV_t} \approx \frac{W}{L} \mu_e V_t^2 \sqrt{\frac{\varepsilon_{Si} q N_A}{2|V_{BS}|}} \quad e^{\{-V_T\}/nV_t}$$

Scaling all the factors, we find that  $I_{Doff}$  and  $P_{static}$  scale poorly!

$$I_{D,off} \rightarrow SI_{D,off} e^{\left\{ \left(1 - \frac{1}{s}\right)V_T\right\} / nV_t} \qquad P_{Static} = V_{DD}I_{D,off} \rightarrow P_{Static} e^{\left\{ \left(1 - \frac{1}{s}\right)V_T\right\} / nV_t}$$

\* We're talking n-channel here, but similar results are found for the p-channel MOSFETs.

## Scaling Rules, cont. - static power scales badly, but...

Static power density's scaling is even worse:

## Scaling Rules, cont. - What about velocity saturation?

Do the same constant E-field scaling by 1/s:

$$L_{\min} \to L_{\min} / s \qquad W \to W / s \qquad t_{ox} \to t_{ox} / s \qquad N_A \to s N_A$$

$$V_{DD} \to V_{DD} / s \qquad V_{BS} \to V_{BS} / s \qquad V_T \to V_T / s$$

so  $C_{ox}^* \to s C_{ox}^* \qquad K \to s K$

Examining our expressions when velocity saturation is important we find:

$$\tau \propto \frac{L_{\min} V_{DD}}{s_{sat} \left[ V_{DD} - V_{Tn} \right]} : \qquad \tau \rightarrow \tau / s$$

$$P_{dyn} = 3n W_{\min} L_{\min} C_{ox}^* V_{DD}^2 f : \qquad P_{dyn} \rightarrow P_{dyn} / s^2$$

$$PD_{dyn @ f_{\max}} = \frac{s_{sat} \varepsilon_{ox} V_{DD} \left[ V_{DD} - V_{Tn} \right]}{t_{ox} L_{\min}} : \qquad PD_{dyn @ f_{\max}} \rightarrow PD_{dyn @ f_{\max}} \rightarrow PD_{dyn @ f_{\max}}$$

Amazingly, there is no difference in the scaling behavior of the gate delay, average power, or power density in this case!

11/5/09 Note: Velocity saturation is not a factor in I<sub>D.off</sub>.

Lecture 1

**Clif Fonstad**, 11/5/09

Lecture 16 - Slide 19

# An historical scaling example - Inside Intel

| <u>Parameter</u>                       | <u>386</u> | <u>486</u> | <b>Pentium</b> |

|----------------------------------------|------------|------------|----------------|

| Scaling factor, s                      | 1          | 2          | 3              |

| L <sub>min</sub> (µm)                  | 1.5        | 0.75       | 0.5            |

| W <sub>n</sub> (μm)                    | 10         | 5          | 3              |

| t <sub>ox</sub> (nm)                   | <b>30</b>  | 15         | 9              |

| <b>V</b> <sub>DD</sub> <b>(V)</b>      | 5          | 3.3        | 2.2            |

| <b>V</b> <sub>T</sub> <b>(V)</b>       | 1          | -          | -              |

| Fan out                                | 3          | 3          | 3              |

| <b>Κ (μΑ/V²)</b>                       | 230        | 450        | 600            |

| GD (ps)                                | 840        | 400        | <b>250</b>     |

| f <sub>max</sub> (MHz)                 | 29         | <b>50</b>  | 100            |

| P <sub>ave</sub> /gate (mW)            | 92         | <b>23</b>  | 10             |

| Density<br>(kgates/cm² @ 20W/cm² max.) | 220        | 880        | 2,000          |

Clif Fonstad, 11/5/09 Sources: Prof. Jesus del Alamo and Intel Lecture 16 - Slide 20

# An second look inside Intel - a slightly different perspective

| <u>Parameter</u>       | <u>486</u> | Pentium generations |               |               |

|------------------------|------------|---------------------|---------------|---------------|

| Scaling factor, s      | -          | 1                   | 1.6           | 2.3           |

| L <sub>min</sub> (µm)  | 1.0        | <b>0.8</b>          | 0.5           | 0.35          |

| SRAM cell area (µm²)   | -          | 111                 | 44            | 21            |

| Die size (mm²)         | 170        | 295                 | 163           | 91            |

| f <sub>mzx</sub> (MHz) | 38         | <b>66</b>           | 100           | 200           |

| t <sub>ox</sub> (nm)   | 20         | 10                  | 8             | 6             |

| <b>Metal layers</b>    | 2          | 3                   | 4             | 4             |

| Planarization          | SOG        | CMP                 | CMP           | CMP           |

| Poly type              | n          | n,p                 | n,p           | n,p           |

| <b>Transistors</b>     | CMOS       | <b>BiCMOS</b>       | <b>BiCMOS</b> | <b>BiCMOS</b> |

Source: Dr. Leon D. Yau, Intel, 10/8/96

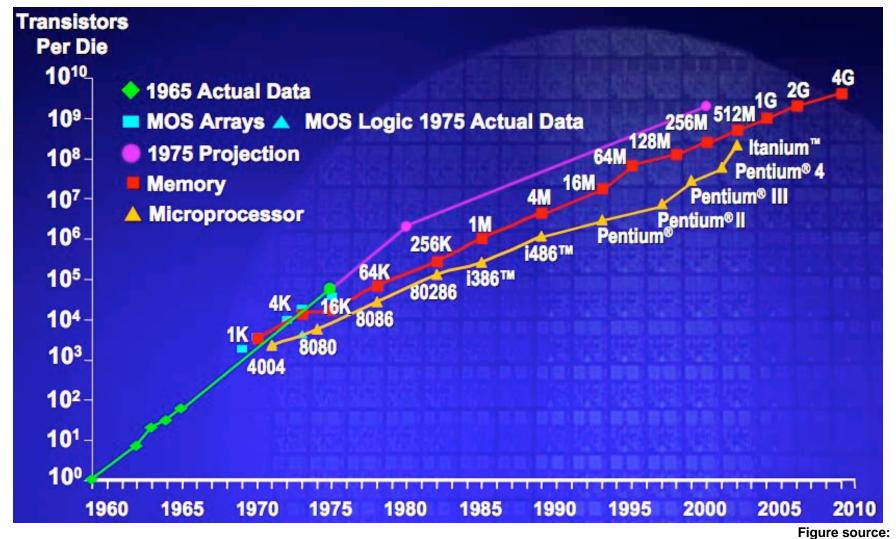

## **Moore's Law** - Everything\* doubles every 2 years.

\* Density, speed, performance, transistors per chip, transistors shipped, transistors per cent, revenues, etc. First stated in 1965 as every year; revised to every 2 years in 1975.

Lecture 16 - Slide 22

Intel Web Site

#### 6.012 - Microelectronic Devices and Circuits

## Lecture 16 - CMOS scaling; The Roadmap - Summary

## CMOS gate delay and power

Three key performance metrics: (We want to make them all smaller)

$$\begin{split} &\text{Gate Delay} = 12 \text{ n } L_{\text{min}}{}^2 \text{ V}_{\text{DD}} / \text{ } \mu_e (\text{V}_{\text{DD}} \text{ - V}_{\text{T}}){}^2 \\ &\text{P}_{\text{dyn}} @f_{\text{max}} \propto C_L \text{V}_{\text{DD}}{}^2 / \text{GD} = (\text{W}_{\text{n}} / \text{L}_{\text{min}}) \text{ } \mu_e \text{C}^*_{\text{ox}} \text{ V}_{\text{DD}} (\text{V}_{\text{DD}} \text{ - V}_{\text{T}}){}^2 / 4 \\ &\text{PD}_{\text{dyn,max}} \propto \text{P}_{\text{dyn}} @f_{\text{max}} / \text{W}_{\text{n}} \text{L}_{\text{min}} = \text{ } \mu_e \epsilon_{\text{ox}} \text{V}_{\text{DD}} (\text{V}_{\text{DD}} \text{ - V}_{\text{T}}){}^2 / 4 \text{ } t_{\text{ox}} \text{L}_{\text{min}}{}^2 \end{split}$$

## CMOS scaling rules

Summary of rules: Constant E-field - scale <u>all</u> dimensions and <u>all</u> voltages by 1/s

The Roadmap; what's next?

Stay tuned: 3-D; new semiconductors; performance over size

MIT OpenCourseWare http://ocw.mit.edu

6.012 Microelectronic Devices and Circuits Fall 2009

For information about citing these materials or our Terms of Use, visit: http://ocw.mit.edu/terms.