MIT OpenCourseWare http://ocw.mit.edu

6.004 Computation Structures Spring 2009

For information about citing these materials or our Terms of Use, visit: http://ocw.mit.edu/terms.

## **Building the Beta**

## <u>Problem 1.</u> Beta quickies:

- A. **†** In an unpipelined Beta implementation, when is the signal RA2SEL set to "1"?

- B. In an unpipelined Beta implementation, when executing a BR(foo,LP) instruction to call procedure foo, what should WDSEL should be set to?

- C. The minimum clock period of the unpipelined Beta implementation is determined by the propagation delays of the data path elements and the amount of time it takes for the control signals to become valid. Which of the following select signals should become valid first in order to ensure the smallest possible clock period: PCSEL, RA2SEL, ASEL, BSEL, WDSEL, WASEL?

<u>Problem 2.</u> Notta Kalew, a somewhat fumble-fingered lab assistant, has deleted the opcode field from the following table describing the control logic of an unpipelined Beta processor.

| PCSEL | RA2SEL | ASEL | BSEL | WDSEL | ALUFN | WR | WERF | WASEL |

|-------|--------|------|------|-------|-------|----|------|-------|

| 0     | -      | 0    | 1    | 1     | A-B   | 0  | 1    | 0     |

| Z?1:Q | -      | ı    | -    | 0     | -     | 0  | 1    | 0     |

| 0     | -      | 1    | -    | 2     | A     | 0  | 1    | 0     |

| 0     | 0      | 0    | 0    | 1     | CMPEQ | 0  | 1    | 0     |

| 0     | 1      | 0    | 1    | -     | ADD   | 1  | 0    | 0     |

- A. ★ Help Notta out by identifying which Beta instruction is implemented by each row of the table.

- B. Notta notices that WASEL is always zero in this table. Explain briefly under what circumstances WASEL would be non-zero.

- C. X Notta has noticed the following C code fragment appears frequently in the benchmarks:

The pointer variable p contains the address of a dynamically allocated array of integers. The value of p[i] is stored at the address Mem[p]+4\*Mem[i] where p and i are locations containing the values of the corresponding C variables. On a conventional Beta this code fragment is translated to the following

instruction sequence:

```

LD(...,R1)  /* R1 contains p, the array base address */

LD(...,R2)  /* R2 contains I, the array index */

...

SHLC(R2,2,R0)  /* compute byte-addressed offset = 4*i */

ADD(R1,R0,R0)  /* address of indexed element */

LD(R0,0,R3)  /* fetch p[i] into R3 */

```

Notta proposes the addition of an LDX instruction that shortens the last three instructions to

```

SHLC(R2,2,R0) /* compute byte-addressed offset = 4*i */

LDX(R0,R1,R3) /* fetch p[i] into R3 */

```

Give a register-transfer language description for the LDX instruction. Examples of register-transfer language descriptions can be for other Beta instructions in the Beta Documentation handed out in lecture.

- D. \* Using a table like the one above specify the control signals for the LDX opcode.

- E. It occurs to Notta that adding an STX instruction would probably be useful too. Using this new instruction, p[i] = j might compile into the following instruction sequence:

```

SHLC(R2,2,R0) /* compute byte-addressed offset = 4*i */

STX(R3,R0,R1) /* R3 contains j, R1 contains p */

```

Briefly describe what modifications to the Beta datapath would be necessary to be able to execute STX in a single cycle.

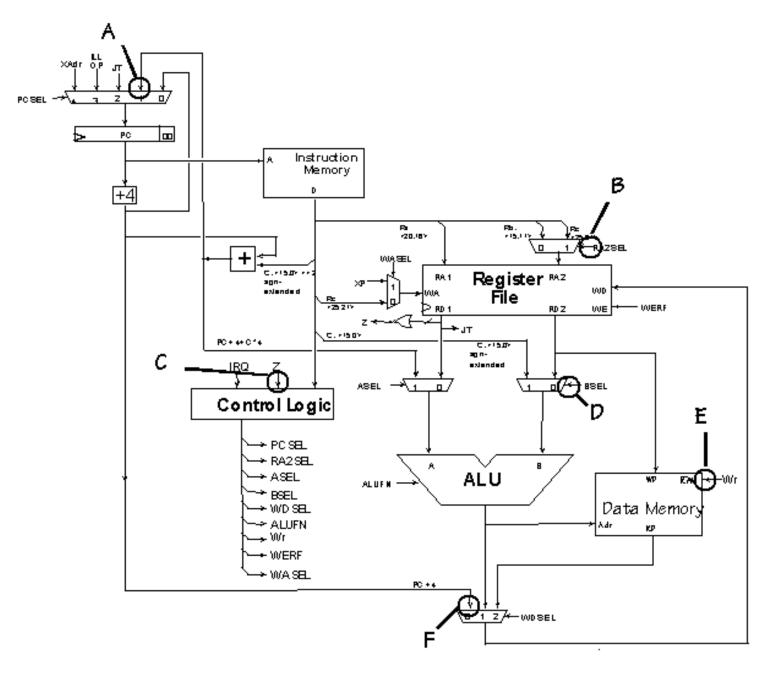

<u>Problem 3.</u> One Beta manufacturer is having quality-control problems with their design. In particular, they've had reliability issues with various device connections that are circled in the attached diagram.

Your job is to write some test programs to help determine if a machine is fault-free. Assume that when a device connection is "faulty," the indicated bus or signal is always "stuck-at 0" instead of the expected value. For each of the circled connections, write an instruction sequence that when executed for a specified number of cycles would indicate whether the connection was okay by leaving a "1" in R0 and leaves some other value in R0 if the connection was faulty. You can assume that all registers are reliably set to 0 before each sequence is executed.

Give your instruction sequence for each of the six indicated faults and briefly explain how each sequence detects the fault and produces something besides "1" in R0 when the fault is present.

- A. **★** Fault A: Input 1 of PCSEL mux stuck at 0.

- B. **\*** Fault B: RA2SEL mux control signal stuck at 0.

- C. **\*** Fault C: Z input to control logic stuck at 0.

- D. Fault D: BSEL mux control signal stuck at 0.

- E. Fault E: WR memory control signal stuck at 0.

- F. Fault F: Input 0 of WDSEL mux stuck at 0.

<u>Problem 4.</u> Flaky Beta's, Inc. has an interesting business plan: they buy -- very cheaply -- Beta processors manufactured by other companies with slight defects and market them as implementing "variants" of the Beta Instruction Set Architecture. FBI's plan is simply to change the documentation of the instructions affected by the manufacturing flaws in each machine, presuming that its customers can live with the revised machine behavior.

The FB1 and FB2 are based on a non-pipelined Beta. They perform exactly as a fully functional non-pipelined Beta (see diagrams at the end of the quiz), except for the following flaws:

The FB1 has the select input to the ASEL mux stuck at 0, causing the register file to always be selected as the A (left) input to the ALU.

The FB2 has the select input to the RA2SEL mux stuck at 0, causing the Rb field of the instruction to always be selected as the RA2 (right) address input to the register file.

Note that, aside from the above flaws, the defective processors behave identically to their fully-functional counterparts; control signals, for example, are generated as for a working Beta processor.

FBI tests both the FB1 and FB2 on six Beta instructions: LDR, ST, SUBC, BNE, LD and JMP. They find that each of the flaws affects only one of the six instructions.

- A. Which Beta instructions does the FB1 flaw affect? Which Beta instructions are affected by FB2 flaw?

- B. Of course many programs use all the instructions in the Beta ISA, so clients need to know if it is possible to rewrite their programs so that they perform the same computation whether they run on an unflawed Beta or an FBI processor. It's okay if the rewritten program takes a different number of instructions than the original. When answering the questions below, assume that rewritten programs still fit in the available memory.

Is it possible to rewrite an arbitrary program so that it will perform correctly on both an unflawed Beta and an FB1?

C. Is it possible to rewrite an arbitrary program so that it will perform correctly on both an unflawed Beta and an FB2?

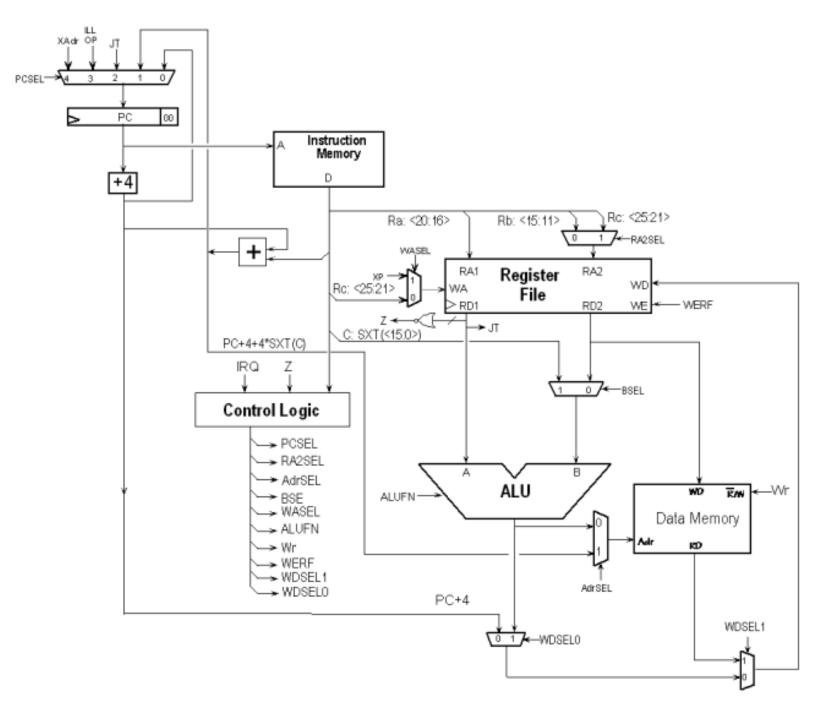

<u>Problem 5.</u> A 6.004 student, Pete Coshaver, has suggested the following modified Beta design to minimize the critical path in his unpipelined implementation.

- A. Briefly describe the differences between the modified Beta shown above and the Beta described in lecture.

- B. Which instructions have their critical path reduced as a result of Pete's modifications?

- C. On a given instruction Pete's control logic generates the following control signals. What is the most likely opcode of instruction being executed?

| PCSEL  | 0 |

|--------|---|

| RA2SEL | _ |

| BSEL   | 1 |

| ALUFN  | + |

| Wr     | 0 |

```

WERF 1

WASEL 0

AdrSEL 0

WDSEL1 1

WDSEL0 -

```

- D. What impact does Pete's redesign of the write-data-select multiplexer (controlled by the WDSEL0 and WDSEL1 control lines) have on the original Beta design?

- a. Pete's old Beta control ROM will not work with his modified Beta design

- b. It requires the BOOL unit of the ALU to be redesigned.

- c. It is most likely slower than the 3-input multiplexer used in the original Beta.

- d. It has no impact; it is functionally identical to the original design.

- e. Some standard Beta instructions can no longer be implemented with Pete's changes.

- E. What is the most appropriate setting of the WDSEL0 and WDSEL1 control lines when executing a BEQ instruction?

- F. Pete would like to connect the ASEL signal of his old Beta design to the AdrSEL signal in his new design. For what Beta instruction type is it necessary for Pete to change the contents of his control ROM before his modified Beta will behave identical to the original version?

- G. Pete was also able to reduce the size of his control logic by merging the functions of two signals into a single output signal. What two signals, from the list given below, could he have merged?

- a) WDSEL0 and WDSEL1

- b) WDSEL0 and WERF

- c) AdrSEL and WASEL

- d) BSEL and RA2SEL

- e) AdrSEL and WR

- H. The minimum clock period of Pete's unpipelined Beta implementation is determined by the propagation delays of the data path elements and the amount of time it takes for the control signals to become valid. Which select signal(s) should become valid first in order to ensure the smallest possible clock period?

## Problem 6. Consider the following potential additions to the Beta Instruction set:

- A. Specify the control signals configurations needed to execute these instructions on an unpipelined Beta.

- B. Explain why the following instructions cannot be added to our Beta instruction set without further modifications: